电容降压电路,作为一种简单、低成本的非隔离式降压方案,常被用于小功率、低成本、对安全隔离要求不高的场合,如LED驱动、小家电控制电源等。其核心在于利用电容在交流电路中的“容抗”特性来限制电流和降低电压,而非传统的变压器或开关电源芯片。其设计也伴随着效率、稳定性和安全性的挑战。本文将深入剖析电容降压电路设计的核心要点,帮助工程师规避常见陷阱。

一、 核心原理:电容的容抗与限流

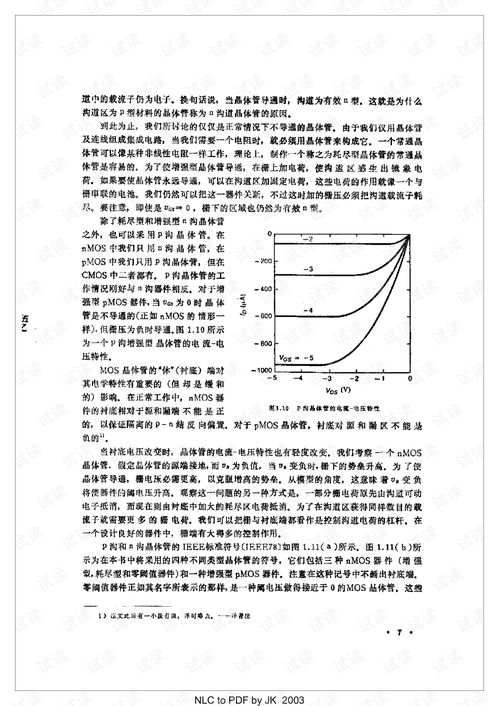

交流电通过电容器时,电容器对交流电呈现的阻碍作用称为“容抗”(Xc),单位为欧姆。其计算公式为:Xc = 1 / (2πfC)。其中,f为交流电频率(如50Hz),C为降压电容的容值(法拉)。

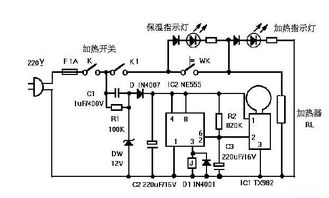

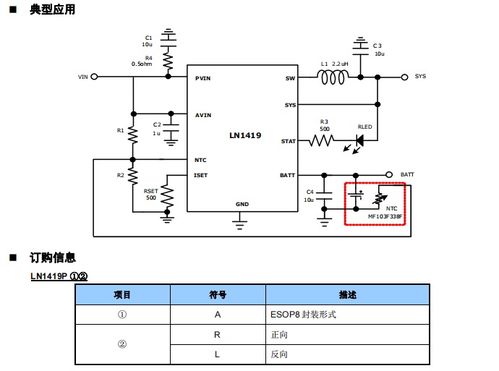

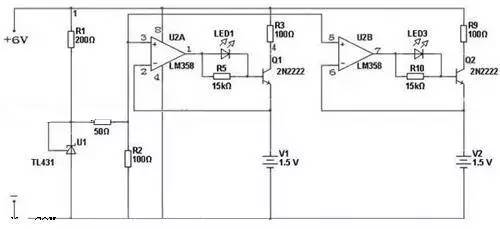

电路的核心在于,这个容抗与后级负载(通常经过整流、滤波和稳压)串联,共同分担了交流输入电压。通过选择合适的电容C,可以控制流过电路的总电流(近似为 I ≈ V_in / Xc),从而实现降压和限流。输出电压则主要由后级的稳压器件(如稳压二极管或线性稳压芯片)决定。

二、 电路设计的四大核心要点

- 降压电容(C1)的选择与安全

- 容值计算:根据目标负载电流I和输入电压Vin、频率f,从容抗公式反推:C ≈ I / (2πf * (Vin - V_out))。这是设计的起点。

- 电容类型:必须使用专为交流电路设计的安规电容(X2或Y2类)。普通电解电容或瓷片电容不能承受持续的交流电压冲击,有爆炸风险。安规电容具有自愈特性,失效时开路而非短路,安全性更高。

- 耐压值:考虑到交流峰值电压和可能的浪涌,耐压值应至少为交流输入电压有效值的2.5倍以上(如220VAC输入,建议选用耐压400VAC或更高的电容)。

2. 泄放电阻(R1)的不可或缺性

降压电容在断电后,两端会残留高压,存在触电危险。必须并联一个高阻值(通常500KΩ至2MΩ)、高耐压的泄放电阻,在断电后数秒内将电容上的电荷释放掉。这是保障人身安全的关键设计。

- 整流、滤波与稳压环节

- 整流桥:通常使用全桥整流,将交流变为脉动直流。二极管的耐压和电流需留有余量。

- 滤波电容(C2):用于平滑整流后的电压,其容值影响输出电压的纹波大小。

- 稳压器件:这是决定最终输出电压稳定性的关键。对于小电流负载,常用稳压二极管(齐纳二极管)进行简单稳压;对于电流稍大或要求更高的场合,可使用线性稳压芯片(如78L05)。需注意稳压器件本身的功耗(压降×电流),防止过热。

4. 电流与功率的严格限制

电容降压电路本质上是恒流源特性,输出电流能力有限,且不提供电气隔离。通常只适用于输出电流在100mA以下的恒流或小功率场景。输出功率越大,电容体积、泄放电阻功耗、稳压器件散热等问题会急剧放大,得不偿失。

三、 重要注意事项与局限性

- 无隔离,危险!:电路直接与市电相连,整个输出端都可能带有高压。绝对不能用于人体可能直接接触的场合,且产品外壳必须可靠绝缘。

- 对负载变化敏感:本质是恒流源,负载变化时,输出电压会随之变化(除非稳压环节足够强大)。不适合负载动态变化剧烈的应用。

- 效率问题:部分电压和功率消耗在降压电容的容抗和稳压器件上,效率通常低于开关电源。

- 电磁干扰(EMI):由于直接接入电网,可能产生一定的传导干扰,对电磁兼容性(EMC)有要求的应用需谨慎评估并增加滤波措施。

四、 与“软件开发”的类比启示

如同软件开发中“选择合适的基础架构决定了系统的性能和可维护性”,在硬件电路设计中,选择电容降压方案这一“架构”时,就必须清晰认知其适用场景(小功率、低成本、非接触)、内在约束(电流有限、无隔离)和必须遵守的“安全规范”(使用安规电容、加泄放电阻)。忽视这些核心要点,就像在软件中忽略内存管理或异常处理一样,会导致系统不稳定甚至灾难性后果。设计,无论是硬件还是软件,其核心都在于深刻理解所用工具的原理与边界,并在约束内做出可靠、安全的实现。

电容降压电路设计,关键在于精确计算容抗、强制使用安规电容、务必添加泄放电阻、合理配置稳压环节,并始终牢记其非隔离、小功率的应用边界。它是一把锋利但需要小心握持的工具,用对了地方,能极大简化设计、降低成本;用错了地方或设计疏忽,则会带来安全隐患。希望这些核心要点能助您在设计工作中游刃有余。