射频集成电路(RFIC)是现代无线通信、雷达、卫星导航等系统的核心部件。它工作在射频频段(通常为几百kHz到几十GHz),负责信号的发射、接收、变频、放大与调制解调。理解其原理、掌握其应用电路设计方法,并辅以高效的软件开发,是成功构建高性能射频系统的关键。

一、 射频集成电路芯片原理

射频IC的核心在于处理高频模拟信号,其设计原理与低频或数字电路有显著差异,主要挑战包括:

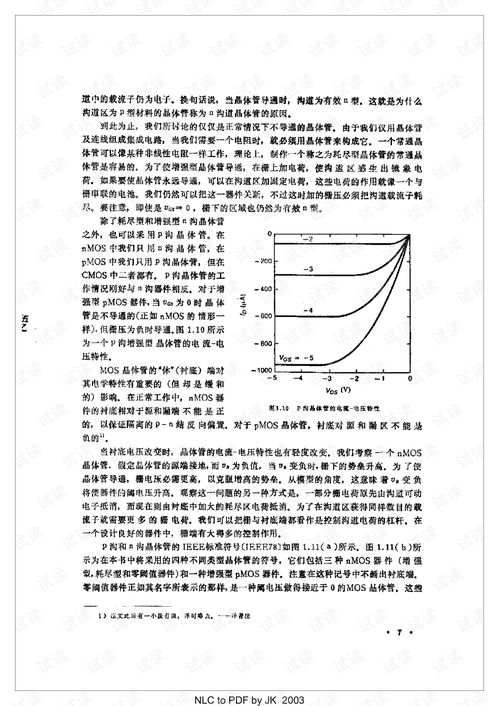

- 分布参数效应:当工作波长与电路物理尺寸可比拟时,导线不再是理想的“短线”,其寄生电感、电容成为不可忽略的分布参数,必须用传输线理论来分析。

- 阻抗匹配:为了最大化功率传输并减少信号反射,射频电路必须在源端、传输线、负载端实现阻抗共轭匹配(通常为50Ω或75Ω标准阻抗)。

- 噪声与非线性:射频放大器、混频器等核心器件会产生内部噪声(如热噪声、闪烁噪声),并表现出非线性特性(如增益压缩、交调失真),这些直接影响系统的灵敏度和动态范围。

- 电磁兼容与隔离:高频信号容易产生辐射干扰,电路内部各部分(如高功率发射与低噪声接收)之间也需严格隔离,防止信号串扰。

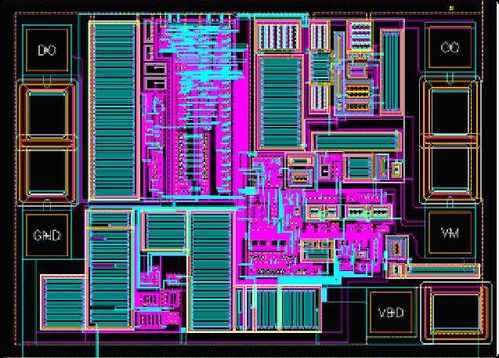

典型的射频IC芯片内部集成有低噪声放大器(LNA)、功率放大器(PA)、混频器(Mixer)、压控振荡器(VCO)、锁相环(PLL)以及滤波器等关键功能模块。

二、 应用电路设计

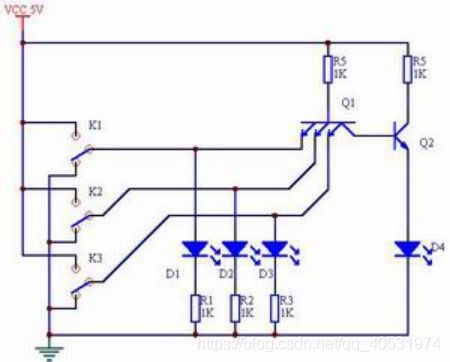

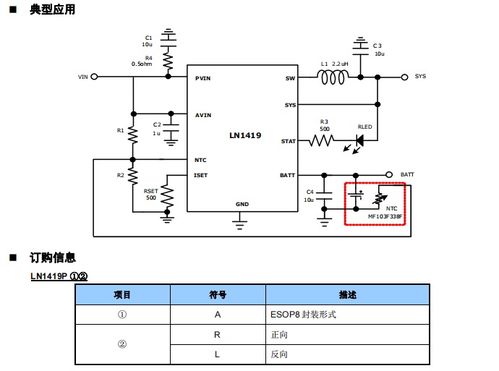

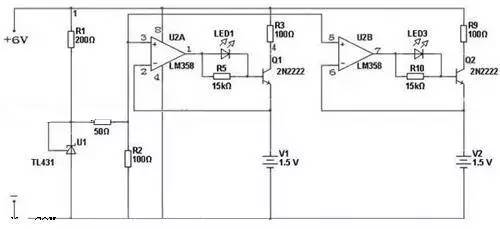

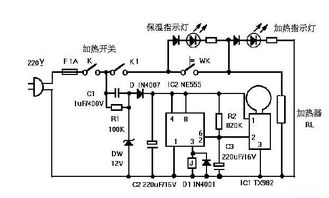

将射频IC芯片应用于具体系统时,外围电路设计至关重要:

- 电源与偏置电路:需提供极其纯净、稳定的直流电源,并设置正确的静态工作点。大量使用去耦电容、磁珠和稳压器来抑制电源纹波和噪声。

- 阻抗匹配网络:使用分立电感、电容或微带线等无源元件,设计匹配网络(如L型、π型),确保芯片端口与天线、滤波器等外部器件间的阻抗匹配。

- 滤波与选频电路:在发射路径抑制带外杂散,在接收路径抑制带外干扰。常采用声表面波(SAW)滤波器、介质滤波器或LC滤波器。

- PCB布局与布线:这是射频设计的“艺术”。必须考虑:

- 分层与接地:采用多层板,提供完整的地平面,实现良好的信号回流路径。

- 微带线控制:将关键信号线设计为特性阻抗可控的微带线或带状线。

- 元件布局:高频通路尽量短直,敏感电路与强干扰源物理隔离,充分屏蔽。

三、 软件开发的关键作用

现代射频系统高度依赖软件,软件开发贯穿于设计、测试和最终产品功能实现的全过程:

- 设计与仿真软件:

- 电路级仿真:使用ADS、Cadence AWR等工具进行原理图仿真、S参数分析、谐波平衡分析和电磁仿真,预测电路性能。

- 系统级仿真:使用MATLAB/Simulink、SystemVue等建立通信链路模型,进行误码率、动态范围等系统级指标验证。

- 芯片配置与控制软件:

- 通过SPI、I2C等数字接口对射频IC内部的寄存器进行编程,动态配置其工作频率、增益、带宽、功耗模式等参数,实现软件定义无线电(SDR)的部分功能。

- 测试与校准软件:

- 在生产和研发测试中,编写自动化测试程序(通常基于LabVIEW、Python或C#),控制矢量网络分析仪、频谱分析仪、信号源等仪表,大规模、高效率地测量射频参数。

- 开发校准算法,补偿因元器件公差、温度变化引起的性能偏差,提升产品一致性和可靠性。

- 信号处理与协议栈软件:

- 在基带处理器(如FPGA、DSP)上,实现数字上变频/下变频、滤波、调制解调、编码解码等算法。

- 运行蓝牙、Wi-Fi、4G/5G等具体的通信协议栈,使射频硬件能够完成实际的通信任务。

结论

射频集成电路的应用是一个将芯片物理特性、电路板级工程设计和多层次软件开发深度融合的复杂过程。设计师必须同时精通高频电磁场理论、模拟电路设计原则以及相关的软件工具与编程技能。从精确的仿真建模、严谨的板级实现,到灵活的芯片配置与强大的信号处理,每一个环节都不可或缺。只有将这三者有机结合,才能将一颗高性能的射频IC芯片的潜力充分发挥出来,打造出稳定、高效、智能的现代无线设备。