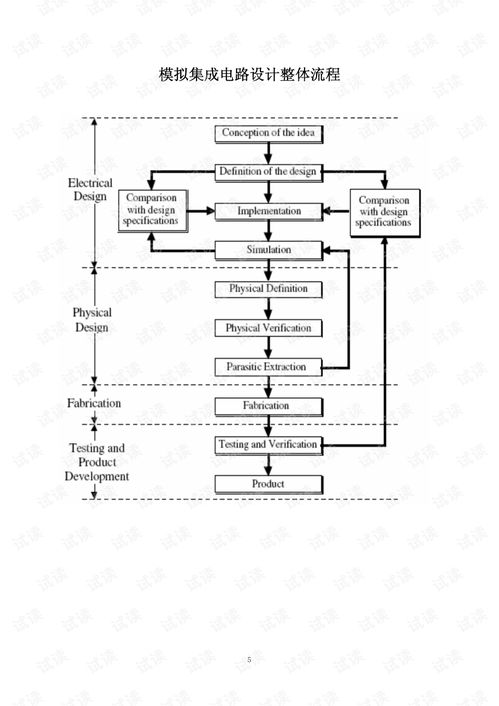

在前两篇笔记中,我们完成了反相器电路图的设计与电路仿真,验证了其逻辑功能与基本性能。本笔记将进入模拟集成电路设计的核心环节之一——物理实现,即使用Cadence Virtuoso完成反相器的版图(Layout)设计,并进行至关重要的版图后仿真(Post-Layout Simulation),以验证物理实现后的电路性能是否满足设计预期。

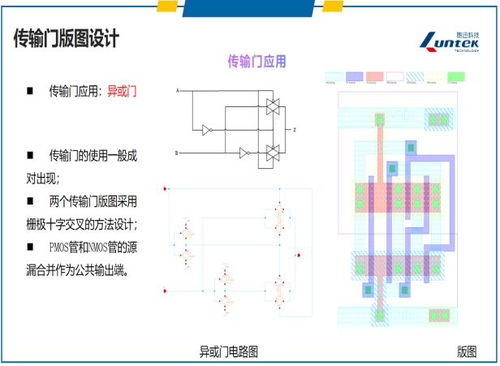

一、 版图设计:将电路图转化为物理图形

版图是集成电路的“物理蓝图”,它定义了每一层掩模(如扩散层、多晶硅层、金属层等)上的几何形状。设计目标是:

- 功能正确性:精确实现反相器(一个PMOS和一个NMOS)的电气连接。

- 设计规则检查(DRC):必须符合晶圆厂提供的物理设计规则(如最小线宽、间距、包围等),否则无法正确制造。

- 面积优化:在满足规则和性能的前提下,尽可能减小芯片面积。

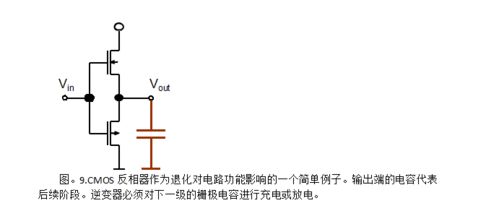

- 性能考量:版图寄生参数(如电阻、电容)会影响电路速度与功耗。

设计步骤简述:

1. 创建版图单元:在Library Manager中,为之前设计的“inverter”电路单元创建一个对应的版图视图(Layout)。

2. 调用并放置器件:

* 从PDK库中调用NMOS和PMOS的版图器件(通常为pcell),根据电路图尺寸(如前仿设定的W/L)实例化。

- 注意PMOS需要放入N阱(N-well)中,而NMOS在P衬底上。需先绘制或调用合适的N阱。

- 布局与布线:

- 布局:合理摆放两个晶体管,考虑电源线(VDD)、地线(GND)、输入(IN)、输出(OUT)的走线路径。通常将PMOS和NMOS的栅极对齐以便连接输入,二者的漏极对齐以便连接输出。

- 布线:使用金属层(如Metal1)绘制导线,连接晶体管的源极、漏极、栅极以及电源、地、输入输出端口。

- 添加接触孔(Contact)和通孔(Via):在需要连接的不同层之间(如多晶硅到金属1,扩散区到金属1)放置接触孔;在不同金属层之间放置通孔。

- 添加引脚(Pin):在输入、输出、电源、地的金属线上,用

text层添加标识(如IN,OUT,VDD,GND),并指定其端口类型(input,output,inout)。 - 运行DRC检查:使用

Verify->DRC工具,选择工艺对应的规则文件。仔细修正所有DRC错误,直至报告“clean”。

二、 电气规则检查(LVS)与寄生参数提取

完成DRC后,版图只是一个符合制造规则的图形,我们需要验证它是否与原始电路图在电气连接上一致。

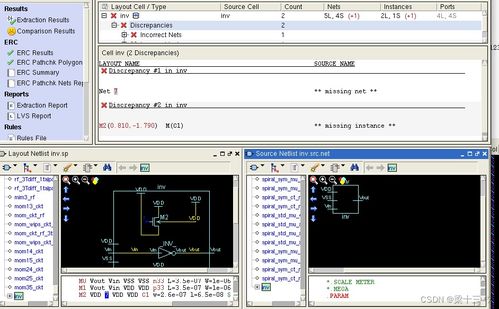

- LVS(Layout vs. Schematic):

- 工具(如Calibre)会将版图提取成一个网表(提取出的晶体管及其连接关系),并与原始电路图网表进行比较。

- 运行LVS(

Verify->LVS),确保“Netlists match successfully”。如果失败,需根据报告逐项排查连接错误、器件匹配错误或引脚命名错误。

- 寄生参数提取(PEX):

- 这是后仿真的基础。真实的版图中,金属连线并非理想导体,它们存在寄生电阻(R)和寄生电容(C)。

- 运行PEX工具(通常在LVS工具中或单独提取工具),根据工艺文件,提取出版图的所有寄生电阻和电容信息,生成一个包含寄生元件的

spice网表(通常后缀为.pex或.sp)。

三、 版图后仿真(Post-Layout Simulation)

这是将物理设计效应纳入仿真的关键一步,结果最接近芯片的实际性能。

- 建立后仿真环境:

- 在Virtuoso ADE(Analog Design Environment)中,新建一个仿真测试。

- 不同于前仿时调用电路图(schematic),此时需要调用PEX提取后生成的寄生参数网表文件作为仿真对象。可以在测试电路中直接包含该网表,或者通过配置仿真库路径来指向它。

- 设置仿真条件:

- 与前仿类似:设置相同的电源电压(如VDD=1.8V)、输入信号(如瞬态分析中的方波脉冲)、工艺角(tt, ss, ff等)、温度等。

- 运行仿真并分析结果:

- 运行瞬态分析,观察输入输出波形。

- 关键对比:将后仿结果与前仿(理想情况)结果叠放在一起对比。通常会观察到:

- 输出波形边沿变缓:由于寄生RC导致充放电速度变慢,上升时间(tr)和下降时间(tf)增加。

- 传播延迟增加:信号从输入到输出的延迟(tpLH, tpHL)明显大于前仿值。

- 波形可能出现轻微过冲或振铃:由于寄生电感和电容的谐振效应。

- 测量关键参数:延迟时间、功耗、噪声容限等,判断是否仍满足设计指标。

- 结果分析与迭代:

- 如果后仿性能下降过多,不满足要求,则需要返回修改版图。常见的优化方向包括:

- 加宽关键路径(如输出节点)的金属线宽,以减少连线电阻。

- 优化布线,缩短关键信号线的长度,以减少寄生电容。

- 重新布局,使连接更紧凑。

- 修改后,必须重新进行DRC、LVS、PEX和后仿真流程,直至性能达标。

四、

从电路图到版图,再到后仿真,是一个完整的“设计-验证-迭代”闭环。版图后仿真是确保设计能够成功流片并工作的最后一道、也是极其重要的仿真验证关口。它揭示了物理实现的真实代价——寄生效应。通过本次反相器的实践,我们初步掌握了在Cadence Virtuoso平台下进行全定制模拟集成电路物理设计与验证的基本流程和核心概念,为后续更复杂电路(如运算放大器、比较器)的设计打下了坚实的基础。记住,优秀的模拟设计工程师必须对版图寄生效应有深刻的直觉和理解。